上一回我们讲到了计算机磁盘的内部结构及其运行原理,今天我们来介绍一下计算机内存的构造以及它的运行机制。 |

|---|

一、存储技术介绍

在开始介绍计算机内存构造之前,我们先来了解一下内存,也就是我们常说的内存条,它到底是怎么样存储数据的,采用的是哪种存储技术。

存储技术:

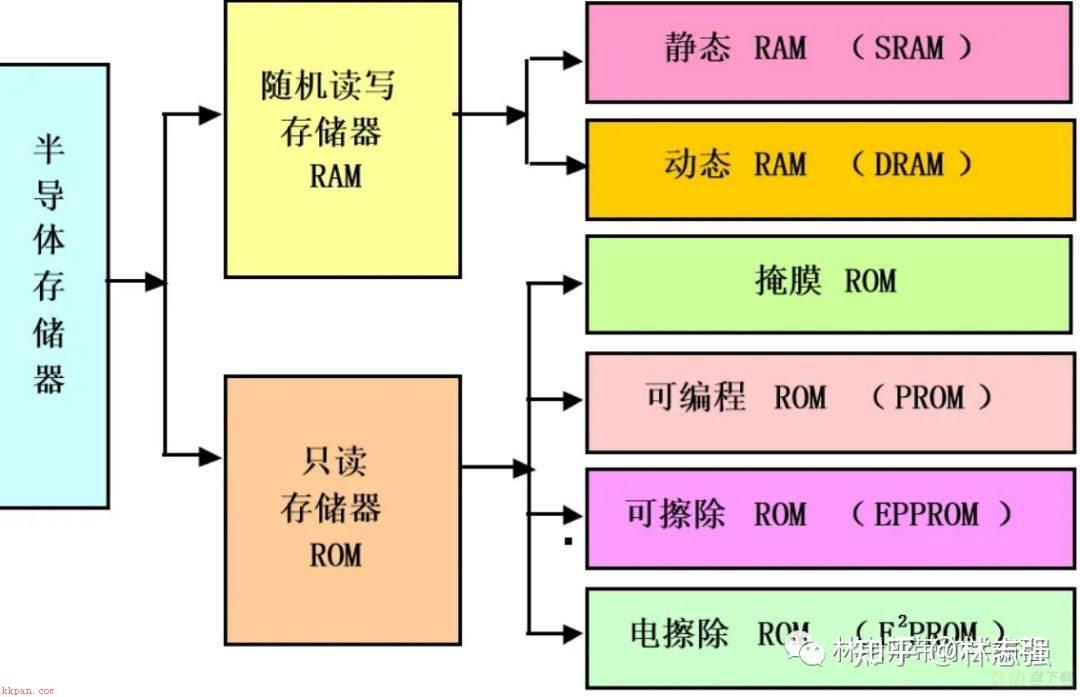

目前主流的存储技术主要是静态存储器(SRAM)、动态存储器(DRAM)、ROM存储器

1.RAM存储器

静态RAM(SRAM)和动态RAM(DRAM)都属于随机访问存储器,静态RAM比动态RAM更快,但是静态RAM不仅价格更贵,而且在同等体积下内存的容量也更小,所以一般被用来做计算机CPU的L2 Cache缓存。而动态RAM(DRAM)就是我们常说的内存条底层存储器了,虽然没有静态RAM(SRAM)速度快,但是在同等体积下,动态RAM(DRAM)可以存储更多的数据,且更便宜。所以目前大部分的计算机内存都是采用动态RAM(DRAM)来实现的。

但是不管是静态RAM(SRAM)还是动态RAM(DRAM),在断电情况下,它们存储的信息都会消失。

2.ROM存储器

只读存储器(Read-Only Memory,ROM)以非破坏性读出方式工作,只能读出无法写入信息。信息一旦写入后就固定下来,即使切断电源,信息也不会丢失,所以又称为固定存储器。ROM所存数据通常是装入整机前写入的,整机工作过程中只能读出,不像随机存储器能快速方便地改写存储内容。ROM所存数据稳定 ,断电后所存数据也不会改变,并且结构较简单,使用方便,因而常用于存储各种固定程序和数据。

百度百科

ROM相对RAM而言,它们最大的区别是:ROM断电之后,仍然可以保存内部的信息,而RAM不行。ROM再经过多次迭代之后,为便于用户使用和大批量生产,进一步发展出可编程只读存储器(PROM)、可擦可编程序只读存储器(EPROM)和带电可擦可编程只读存储器(EEPROM)。其中带电可擦可编程只读存储器(EEPROM)就是我们所熟知的U盘了。

二、DRAM底层存储原理

在介绍完目前主流的存储技术之后,我们开始今天的重头戏计算机内存。上面介绍到,计算机内存也就主存,是采用DRAM存储器实现的,那DRAM存储器内部是怎么实现的呢?它是如何记录0和1的呢?下面我们就来正式介绍一下DRAM存储器底层实现。

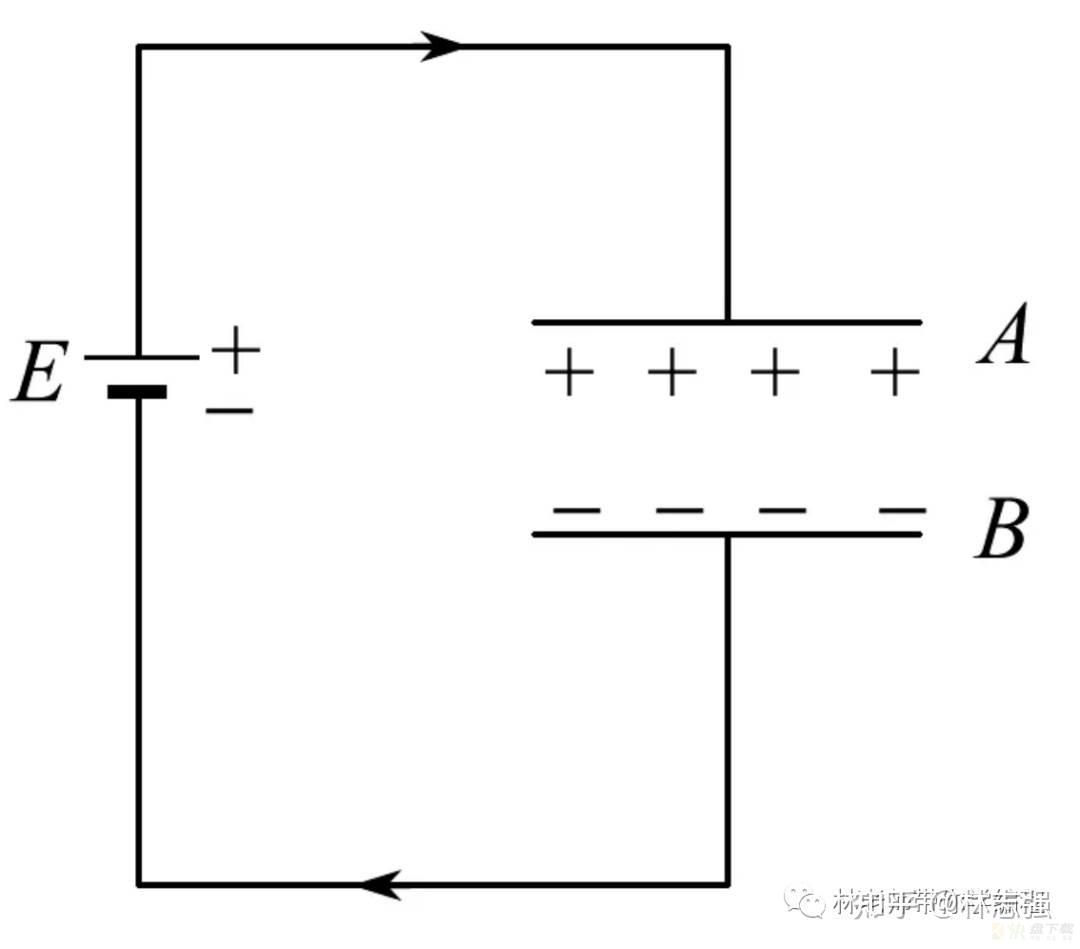

上一章节我们了解到,计算机内部最底层的信息源其实就是电流,通过识别电压,得到0和1,然后将大量的0和1解码为对应的信息。那DRAM必然也是采用一种技术来存储0和1的电压状态,而且相对稳定,可以在一段时间内稳定的维持两种状态,并且这两种状态可以被写入和读取。那DRAM到底是采用什么技术的呢?答案就是电容。

电容(Capacitance)亦称作“电容量”,是指在给定电位差下自由电荷的储藏量,记为C,国际单位是法拉(F)。一般来说,电荷在电场中会受力而移动,当导体之间有了介质,则阻碍了电荷移动而使得电荷累积在导体上,造成电荷的累积储存,储存的电荷量则称为电容。

百度百科

电容加压模型

电容初始状态是不带电荷,我们可以将这种状态定义为0,后面我们给电容充电,电容就会带上正负电荷,因为电容的特性,加压之后断电也可以维持一段时间的电荷在电容中,我们将这种状态标记为1。这样我们就可以采用电容来表示计算机中的0和1。

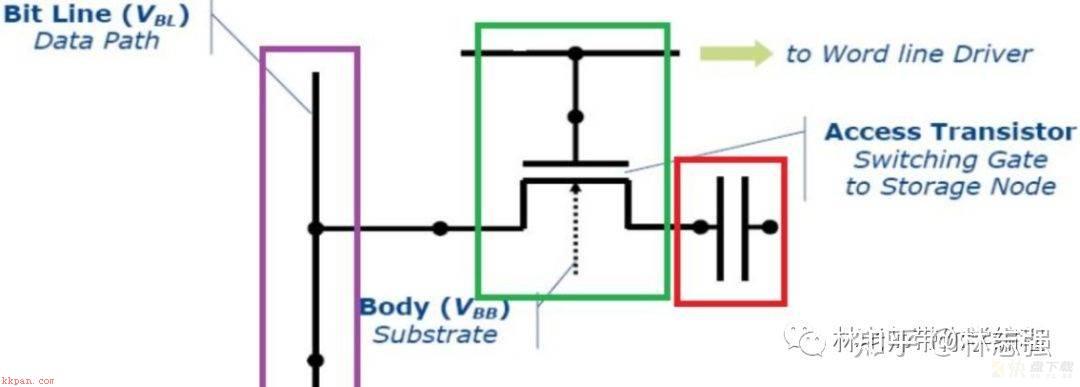

单单有电容想要实现内存的功能肯定是不够的,因为我们需要数据的写入和写出,这里就是需要一个电路结构来实现,我们先从写入说起。我们先来思考一下一个完整的写入过程需要哪些步骤。

写入步骤:

1.第一我们需要数据信号控制器,通过它来控制数据的写入和读取。

2.第二我们需要一个开关,用来控制写入过程的开始和结束。

3.第三就是存储信号的电容了。

接下来我们来看实现这个逻辑的电路图:

DRAM存储单元

图中紫色部分叫做Bit Line,它是上面提到的数据信号控制器,需要写入的数据信号,就是通过这个控件来写入电容的。绿色部分是用来控制电容的写入和读出的,红色部分就是电容。Bit Line负责数据的传递,绿色的Word Line和电晶体负责开关,红色电容负责存储信号,这里就是DRAM存储器的基础了。

DRAM和DDR4的关系介绍:

一般我们买的内存条都是叫做DDR4,好像和DRAM没关系,其实不是,DDR4只是DRAM的一个分支,DRAM有很多的分支,根据结构和技术指标主要分为3种DDR、GDDR、HBM。它们的传输速度(bandwidth)排序大致为HBM>GDDR>DDR。其中我们所熟知的DDR4就是属于DDR的分支。DRAM底层存储原理就介绍到这边,如果大家还想了解更多这方面的知识,可以阅读:关于存储器中DRAM的一些小科普(3) - 知乎

三、内存在计算机中的作用

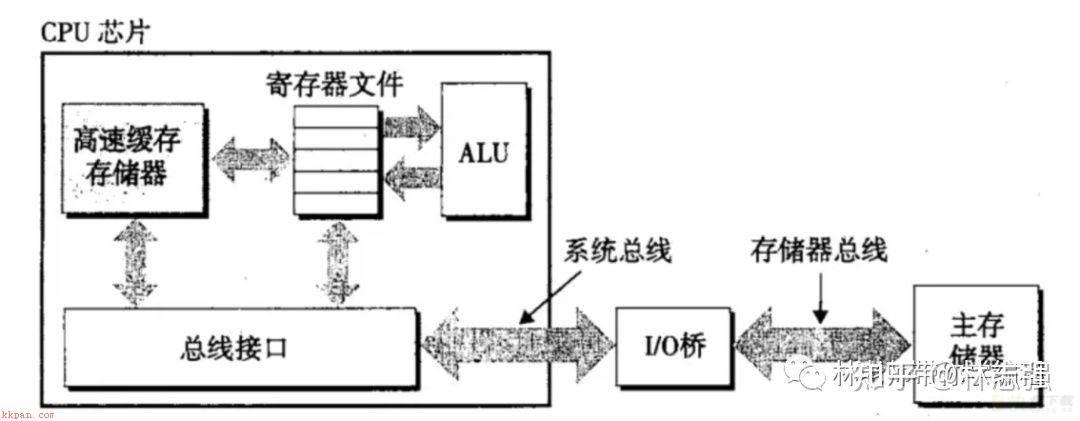

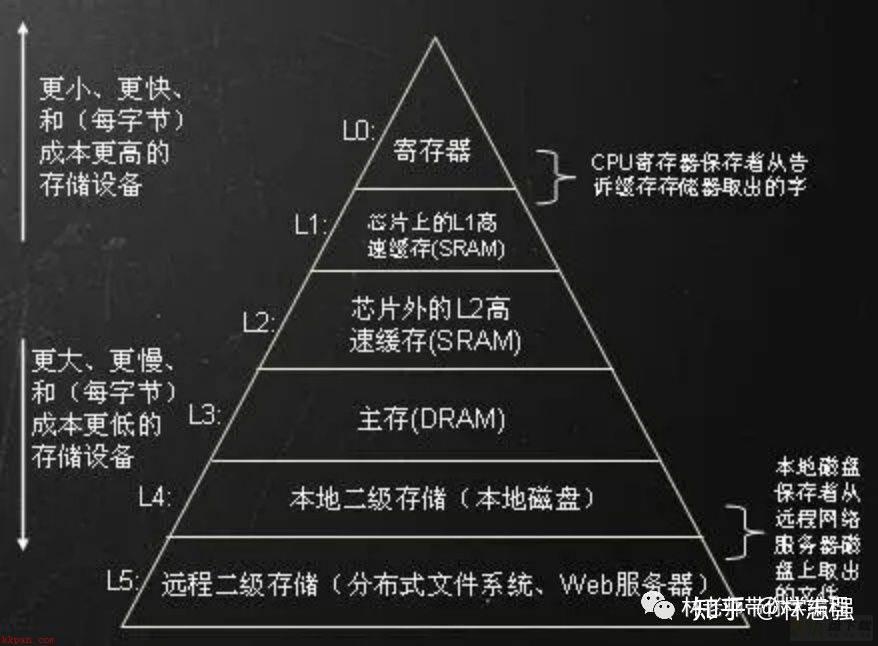

上面我们介绍了内存(又做主存)底层存储结构,那在计算机层面,内存又处于一个什么样的角色?它负责哪些事情呢?如下图所示:

内存又叫主存,从名称可以看出,它是计算机主要存储位置。那有些童鞋就会问,那磁盘的存储空间不是更大嘛。磁盘的存储空间虽然很大,但是计算机的CPU没办法直接跟磁盘交互,它只跟内存打交道。CPU通过总线读写内存的数据,如果数据不在内存中,就会去磁盘中检索对应的数据到内存中,然后返回给CPU。所以内存在计算机中核心的作用就是用来做主缓存,配合CPU读写数据。

四、CPU多级缓存的应用

上一节我们说到内存在计算机中的作用,主要是用来缓存数据,提供给CPU使用。但是CPU运行的速度太快了,相对而言内存的读写速度就非常慢了。如果CPU每次都要等内存操作完成,才可以继续后续的操作,那效率会非常低下。所以为了解决这个问题,CPU内部缓存逐步发展到L1 Cache、L2 Cache、L3 Cache的三级缓存结构,如下图所示:

三级缓存:

L1 Cache,分为数据缓存和指令缓存,逻辑核独占。

L2 Cache,物理核独占,逻辑核共享。

L3 Cache,所有物理核共享。

缓存级别越小,越靠近CPU, 同样也意味着速度越快,但是对应的容量越少。

存储器存储空间大小:内存>L3>L2>L1>寄存器。

存储器速度快慢排序:寄存器>L1>L2>L3>内存。

通过三级缓存结构,可以极大地提高CPU运行效率,但是从方法论上来说,任何一件事情,肯定有好处和坏处。三级缓存结构好处显而易见,可以提高CPU运行效率,不用被内存读写速度慢拖累。但它不好的地方是,这种三级缓存结构,在数据同步方面比较麻烦。特别是多核处理器,在修改缓存数据之后,需要及时同步给其它核的CPU,不然对方读取到的就是脏数据。这也就是我们Java开发常说的内存屏障问题,需要采用volatile关键词来获取最新的数据。有兴趣的童鞋可以阅读:CPU多级缓存架构 - 知乎 。

五、虚拟内存的引入

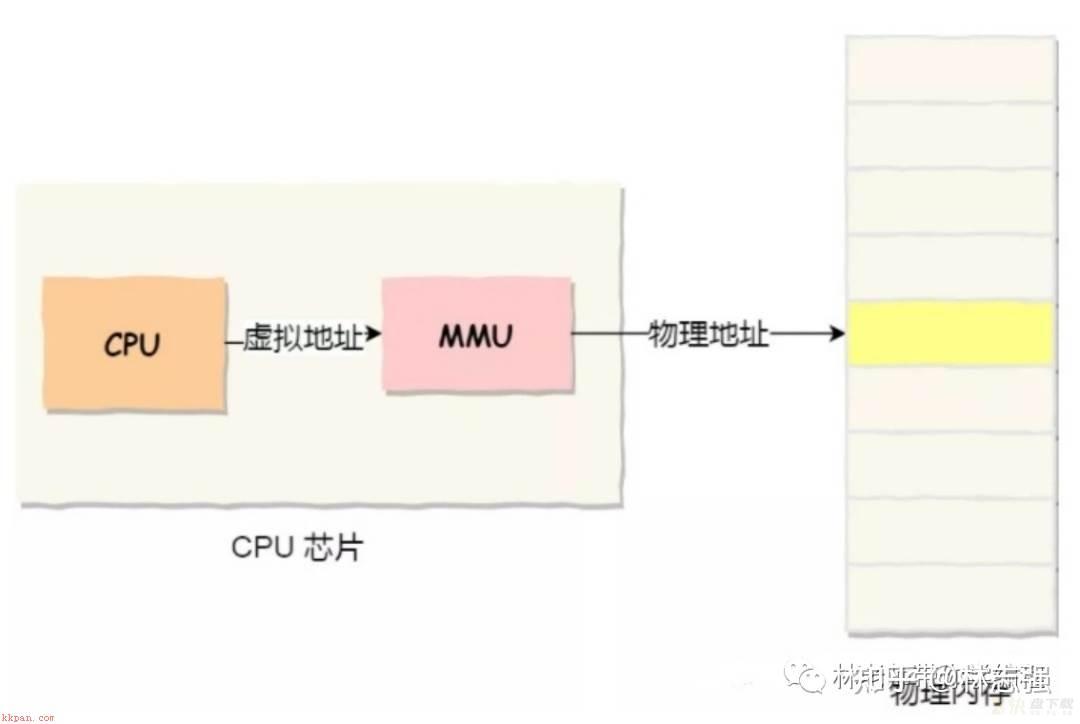

上面讲到了,CPU会读写数据到内存中,那CPU是直接跟内存的实际物理地址交互的嘛?那如果是每个程序都直接跟内存物理地址交互,那就会存在:A程序写入a数据到内存中,同时B程序修改b数据到内存中。因为a和b对应的同一个内存物理地址,所以导致b直接覆盖a的数据。那如果这样的话,整个计算机将会乱套。所以我们的操作系统给出了这个解决方案,就是虚拟内存。

我们先来了解两个概念,如下所示:

虚拟内存地址:我们程序所使用的内存地址叫做虚拟内存地址(Virtual Memory Address)。

物理内存地址:实际存在硬件里面的空间地址叫物理内存地址(Physical Memory Address)。

CPU其实不会直接跟内存物理地址交互,而是通过一个叫做内存管理单元(MMU),来将虚拟地址转为实际的物理地址,如下图所示:

有了这个MMU之后,就不会出现数据互相影响的情况了。操作系统会给每一个进程分配独立的一套虚拟地址,各个进程之间互不干涉。通过虚拟内存来管理实际的物理地址,每一个进程申请的物理地址,因为有虚拟内存的统一管理,所以不会出现互相影响的情况。

虚拟内存的实现形式目前有:内存分段、内存分页或者是二者组合使用。想要了解更多操作系统中虚拟内存知识点,可以阅读:一篇文带你搞懂,虚拟内存、内存分页、分段、段页式内存管理(超详细) - 知乎

六、复盘总结

到这边计算机内存相关知识就分享完毕了,文中我们从内存底层存储技术--》存储原理介绍--》内存在计算机中的作用--》CPU多级缓存的应用--》虚拟内存解决数据互相干涉问题。相信到这里,童靴们对计算机内存会有一个清晰的认识了。

本篇文章主要是起到一个大纲的作用,里面涉及到的知识点:电容(物理)、虚拟内存(操作系统)、多级缓存(CPU构造),都是非常深的知识。如果想要了解更多计算机组成原理的童靴,可以阅读下面2篇文章,看完后,大家对计算机内部组成原理,会有一个更加全面深入的了解。